Product Details

ISBN 10 : 4297123053

Content Description

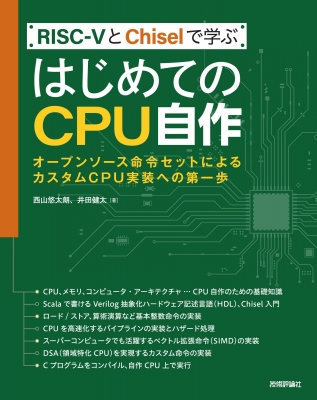

本書では、UCバークレーで開発されたオープンソースの命令セット(ISA)「RISC‐V」を用いて、CPUの作り方を解説します。コンピュータ・アーキテクチャ、ハードウェアに関する知識があまりない方にも理解できるように、基礎からわかりやすく学ぶ構成となっています。CPUとコンピュータ・アーキテクチャのしくみを解説したうえで、基本整数命令の実装から、CPUの高速化で活躍するパイプラインの実装、スーパーコンピュータでも活躍するベクトル拡張命令(SIMD)、さらに汎用CPUでは負荷の高い処理をより高速に実行するためにCPUへ追加可能なカスタム命令の実装までを行います。CPU設計に用いる基本言語としては、Velilogを抽象化したHDL(ハードウェア記述言語)であるChiselを利用しています。CPUの自作範囲に関して、手順が煩雑なFPGAでの動作確認は行わず、ソフトウェア上でのエミュレーションをゴールとしているので、ソフトウェアエンジニアの方にも取っ付きやすいものとなっています。巻末には、昨今RISC‐Vが注目されている理由を整理するため、RISC‐Vのもたらす価値についてまとめています。

目次 : 第1部 CPU自作のための基礎知識(CPUとは何か/ コンピュータ・アーキテクチャ ほか)/ 第2部 簡単なCPUの実装(環境構築/ 命令フェッチの実装 ほか)/ 第3部 パイプラインの実装(パイプラインとは/ パイプラインレジスタの実装 ほか)/ 第4部 ベクトル拡張命令の実装(ベクトル命令とは/ VSETVLI命令の実装 ほか)/ 第5部 カスタム命令の実装(カスタム命令の意義/ ポピュレーションカウント命令の実装 ほか)

【著者紹介】

西山悠太朗 : 1991年生まれ。東京大学卒。株式会社フィックスターズRISC‐V研究所研究員。ウエストバーグ株式会社代表取締役。メディア事業や教育出版事業など複数の事業売却を経験。ビッグデータ解析、WEBマーケティングを軸に、一部上場企業からスタートアップまで幅広く業務支援を行う。また、立ち上げたD2C事業を1年で年商5億円規模まで急成長させる等、toB/toC、有形/無形商材と幅広いビジネス経験を積む。PCメーカー経営をきっかけにコンピュータへの興味が膨らみ、現在はRISC‐V研究に携わる

井田健太 : 1986年生まれ。株式会社フィックスターズRISC‐V研究所研究員。大学院修士課程修了後、半導体後工程の装置メーカーに就職し、装置用組み込みソフトウェアの開発を行う。その後転職を経て、株式会社フィックスターズにて主にFPGAの論理設計とFPGAを制御するためのソフトウェア開発を行う(本データはこの書籍が刊行された当時に掲載されていたものです)

Customer Reviews

Book Meter Reviews

こちらは読書メーターで書かれたレビューとなります。

powered by

kaizen@名古屋de朝活読書会

読了日:2021/12/19

酒井 敦

読了日:2021/11/02

Q

読了日:2021/10/23

(外部サイト)に移動します

Recommend Items

Feedback

Missing or incorrect information?

Product information of this page .